© 2024 Burak Soner

## **ELEC 305**

# **Digital System Design Lab**

Fall 2024

**Lecture 7:** Interfaces

- Interfaces: More than buttons, switches and LEDs (or not?)

- Analog: ADC / DAC

- "Digital" communication protocols: I2C, I2S, UART, SPI, ...

- Graphics: VGA, TFT LCDs, ...

- Basys3 GPIO project

- We've written interface requirements earlier, so what are the interfaces that we know of?

- Buttons: digital input, monostable, we have to keep clicking to make it "stick"

- Switches: digital input, bistable, we snap it once and it "sticks"

- LEDs (incl. 7-seg displays): digital output, voltage controlled

that's about it

• These simple devices were tied to General Purpose Input Outputs (GPIO) on the FPGA

#### Interfaces

- On MCUs we know that GPIO is only one of many digital interfaces

- e.g., Arduino Uno: GPIO, ADC, PWM, UART, I2C and SPI

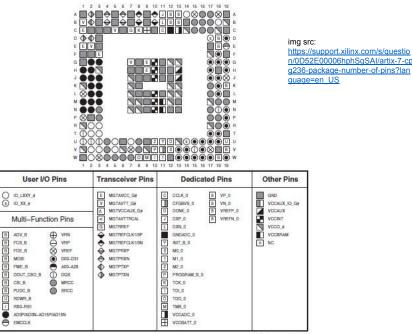

- On the FPGA, other than a few special cases on more expensive FPGAs, there are no interfaces, all IO pins are GPIO.

- The MCUs actually have small circuits for those interfaces. On the FPGA we build these ourselves

CP236 and CPG236 Packages—XC7A15T, XC7A35T, and XC7A50T

ug475\_c3\_301\_011714

Figure 3-41: CP236 and CPG236 Packages—XC7A15T, XC7A35T, and XC7A50T Pinout Diagram

- ...

© 2024 Burak Soner

#### Interfaces

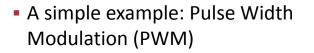

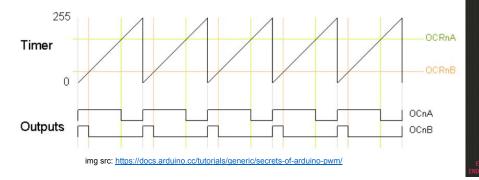

- Typically a fixed frequency "square wave", but the duty cycle (i.e., pulse width) is varied →→

- PWM is practically everywhere:

- dimming lights, controlling motors, ...

- communications (e.g., duty cycle = message content)

img src: https://docs.arduino.cc/tutorials/generic/secrets-of-arduino-pwm/

img src: https://www.thomsonlinear.com/tr/destek/ipuclari/pwm-nedir

#### Interfaces

- On the MCU we generate the PWM waveform by generating an interrupt at timer values that correspond to pulse up and pulse down events

- On the FPGA it's the same principle but no interrupts of course, just the circuit

| <pre>TITY pwm IS GENERIC( sys_clk : INTEGER := 50 000 000;system clock frequency in pwm freq : INTEGER := 100 000;PWM switching frequency in bits_resolution : INTEGER := 8;bits of resolution setting phases : INTEGER := 1);number of output pwms and PORT(</pre>                                                                                                                                                                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| reset_n : IN STD_LOGIC;async<br>ena : IN STD_LOGIClatcl<br>duty : IN STD_LOGIC VECTOR(bits_resolution-1 DOWNTO 0);duty<br>pwm.out : OUT STD_LOGIC VECTOR(phases-1 DOWNTO 0);pwm.0                                                                                                                                                                                                                                                        |  |

| CHITECTURE logic OF pwm IS<br>CONSTANT period : INTEGER := sys_clk/pwm_freq;<br>TVPE contres IS ARRAY (0 TO phases-1) OF INTEGER RANGE 0 TO period - 1;<br>SIGMAL count : counters := (OTHERS => 0);<br>SIGMAL half_duty, w: INTEGER RANGE 0 TO period/2 := 0;<br>TYPE half_duties IS ARRAY (0 TO phases-1) OF INTEGER RANGE 0 TO period/2;<br>SIGMAL half_duty : half_duties := (OTHERS => 0);<br>GIN<br>PROCESS(clk, reset_n)<br>BEGIN |  |

| <pre>bclim<br/>ff(reset_n = '0') THEN<br/>count &lt;= (OTHERS =&gt; 0);<br/>pwm_out &lt;= (OTHERS =&gt; '0');<br/>pwm_n_out &lt;= (OTHERS =&gt; '0');<br/>ELSIF(Clk'EVENT AND Clk = '1') THEN<br/>IF(ena = '1') THEN<br/>half_duty_new &lt;= conv_integer(duty)*period/(2**bits_resolution)/2;<br/>END IF;</pre>                                                                                                                         |  |

| <pre>FOR i IN 0 to phases 1 LOOP FIT(count(0) = period - 1 - i*period/phases) THEN count(i) &lt;= 0; half_duty(i) &lt;= half_duty_new; ELSE count(i) &lt;= count(i) + 1; END IOF; END LOOF;</pre>                                                                                                                                                                                                                                        |  |

| <pre>Chi Luo; the to phases 1 LOOP FOR i IN 0 to phases 1 LOOP If(count(i) = half duty(i)) THEN pym_out(i) &lt;= '0; pym_n out(i) &lt;= '1; ELSIF(Count(i) = period - half_duty(i)) THEN pym_out(i) &lt;= '1; pym_n out(i) &lt;= '0; END This: END FORCES; END PROCESS;</pre>                                                                                                                                                            |  |

| D logic;                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

- Other interfaces are the same! If it's digital, we can build a circuit for it on the FPGA

- As long as the performance criteria allow it of course (sometimes the clock freq at which you have to work with is larger than what your device allows. In that case you're out of luck)

- Also communication interfaces like I2C, I2S, UART, RX232, ... all of these are just GPIOs that are actuated and read according a specific "protocol"

- In summary, we studied GPIOs so far (buttons, LEDs, switches), but other digital interfaces are actually only more contrived versions of the same thing

- I mentioned at the start of the semester → Most interfaces you will run into in this course will already have optimized VHDL modules available online. We'll therefore study the protocols and just use available modules (maybe modify them a bit) and cite those.

#### **Interfaces: Analog**

- We said "if it's digital, we can build a circuit for it on the FPGA", what about analog?

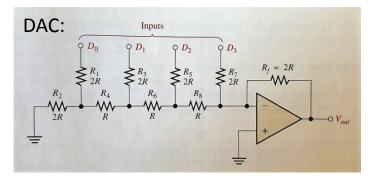

- Interfacing with analog signals requires similar actions, but additional circuitry is needed

- Specifically, an ADC needs at least a sample-and-hold circuit, and a DAC needs something like a resistive ladder

- Designing these circuits for fast operation requires serious expertise

- Processing the sampled versions of the signals is the same as the other digital interfaces we've seen, just "bits moving up and down"

img src: https://www.circuitbasics.com/analog-to-digital-converters/

img src: https://www.circuitcrush.com/digital-analog-converters-tutorial/

ADC:

Clock

## **Interfaces: Analog**

2024 Burak Soner

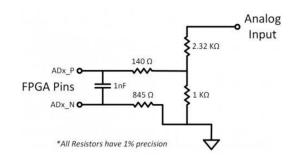

- Can we use this on our boards?

- Yes, Artix-7 has an on-board ADC called XADC on J3

- It's a differential ADC (connect GND to N pin)

- From the reference manual:

- "The XADC core within the Artix-7 is a dual channel 12-bit analog-to-digital converter capable of operating at 1 MSPS. Either channel can be driven by any of the auxiliary analog input pairs connected to the JXADC header."

img src: https://digilent.com/reference/ media/reference/programmable-logic/cmod-a7/cmod a7 rm.pdf

## **Interfaces: Analog**

3 2024 Burak Soner

- XADC is not an RTL module (e.g., debouncer). It's an IP Core Xilinx provides (e.g., DSP48E1)

- Select it from the IP Catalog and just instantiate it

- We configure the rest of our source files to work with it

- I will share a tutorial on this later on. You can use this IP catalog for different cores in your projects

| B. + + B B X I                      | μ o Σ % Ø M                                                                               |                                                                                                                                                                                | 📰 Default Layout 🗸                              |

|-------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Flow Navigator 🗧 🏺 ? _              | PROJECT MARAGER - sampler_thro_system                                                     |                                                                                                                                                                                | ?                                               |

| PROJECT MANAGER                     | Sources ? _ D C ×                                                                         | Project Summary × IP Catalog ×                                                                                                                                                 | 2 0 0                                           |

| Settings                            |                                                                                           | Cores   Interfaces                                                                                                                                                             |                                                 |

| Add Sources<br>Language Templates   | E Design Sources                                                                          | Q ≚ ≑ ≇ 4; ⊁ ∅ ⊕ 0,                                                                                                                                                            |                                                 |

| IP Catalog                          | >  Constraints (1) Constraints (1) Constraints (1) Constraints (1)                        | Search: Q- xadc (2 matches)                                                                                                                                                    |                                                 |

| + ir calaroy                        | ⇒ sim_1                                                                                   | Name ^1 AV4 Status License VLNV                                                                                                                                                |                                                 |

| IP INTEGRATOR                       | > G Utility Sources                                                                       | V 🖙 Vivado Repository                                                                                                                                                          |                                                 |

| Create Block Design                 |                                                                                           | PPGA Features and Design                                                                                                                                                       |                                                 |

| Open Block Design                   |                                                                                           | > G XADC                                                                                                                                                                       |                                                 |

| Generate Block Design               |                                                                                           | XADC Waged AX84, AX84-Stream Production Included xilinx.com/ip:xadc_wiz:3.3                                                                                                    |                                                 |

|                                     |                                                                                           |                                                                                                                                                                                |                                                 |

| ✓ SIMULATION                        | Hierarchy Libraries Compile Order                                                         |                                                                                                                                                                                |                                                 |

| Run Simulation                      | memory Duranes Complete order                                                             |                                                                                                                                                                                |                                                 |

| Y RTL ANALYSIS                      | IP Properties ? _ 🗆 🖾 ×                                                                   |                                                                                                                                                                                |                                                 |

| > Open Elaborated Design            | 🕈 XADC Wizard 🔶 👄 💠                                                                       |                                                                                                                                                                                |                                                 |

|                                     | Version: 3.3 (Rev. 7)                                                                     |                                                                                                                                                                                |                                                 |

| ✓ SYNTHESIS                         | Interfaces: AX04, AX04-Stream                                                             |                                                                                                                                                                                |                                                 |

| Run Synthesis                       | Description: The XADC Wizard generates an HDL                                             | Details                                                                                                                                                                        |                                                 |

| > Open Synthesized Design           | wrapper to configure a single 7 Series FPGA<br>XADC primitive for user-specified channels | Name: XADC Wizard                                                                                                                                                              |                                                 |

|                                     | and alarms.                                                                               | Version: 3.3 (Rev. 7)                                                                                                                                                          |                                                 |

| IMPLEMENTATION                      | Status: Production                                                                        | Interfaces: A04, A04-Stream<br>Description: The XADC Wzard generates an HDL wrapper to configure a single 7 Series FPGA XADC primitive for user-specified channels and alarms. |                                                 |

| Run ampremenation Status Production |                                                                                           | Status: Production                                                                                                                                                             |                                                 |

| > Open Implemented Design           | Vendor: Xilinx.Inc.                                                                       | License: Included                                                                                                                                                              |                                                 |

| PROGRAM AND DEBUG                   |                                                                                           |                                                                                                                                                                                |                                                 |

| Generate Bitstream                  | Tcl Console Messages Log Reports Design Runs ×                                            |                                                                                                                                                                                | ? _ 0 0                                         |

| > Open Hardware Manager             | Q ≚ ≑ 14 ≪ ▶ ≫ + %                                                                        |                                                                                                                                                                                |                                                 |

|                                     |                                                                                           |                                                                                                                                                                                | Report Strategy                                 |

|                                     | ∨ > synth_1 constrs_1 Not started                                                         |                                                                                                                                                                                | Vivado Synthesis Default Reports (Vivado Synthe |

|                                     | ▷ impi_1 constra_1 Not started                                                            | Visado Implementation Defaults (visado Implementation 2019)                                                                                                                    | Vivado Implementation Default Reports (Viva     |

|                                     |                                                                                           |                                                                                                                                                                                |                                                 |

| P: XADC Wizard                      |                                                                                           |                                                                                                                                                                                |                                                 |

## **Interfaces: Digital Comms**

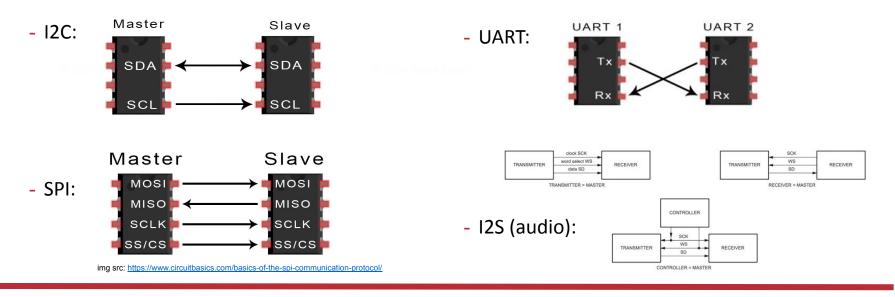

- Digital communication protocols are perhaps the most widely available modules for FPGAs since they are typically platform-independent (XADC is Xilinx's core)

- Examples:

## **Interfaces: Digital Comms**

2024 Burak Sone

- There are many types, characterized by

- How many wires they need

- How they manage collisions (master-slave, ALOHA, ...)

- Reliable speeds / other physical layer characteristics,

- ... © 2024 Burak Soner

- "Users" (ICs) of these protocols usually have addresses on a bus, and the master prevents collisions from happening by letting different slaves speak

- unfortunate terminology, but that's how the protocols are built

- There's no upper bound in complexity to such interfaces, the ones we saw are the simplest. Check PCIe, USB, MIPI, CSI, Ethernet etc. implementations to see how complex these can get.

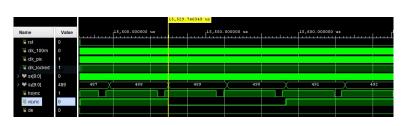

## **Interfaces: Digital Comms**

2024 Burak Sone

- Many of these interfaces are available in VHDL code, and also specifically for Basys3-compatible modules (e.g., Pmod audio interfaces <-> I2S)

- <u>https://forum.digikey.com/t/i2c-master-vhdl/12797</u>

- <u>https://forum.digikey.com/t/i2s-pmod-quick-start-vhdl/13065</u>

- <u>https://forum.digikey.com/t/uart-vhdl/12670</u>

- https://forum.digikey.com/t/spi-master-vhdl/12717

- You don't have to rewrite these in your projects. Just check the documentation to see how they work, use them, cite them, modify them as needed.

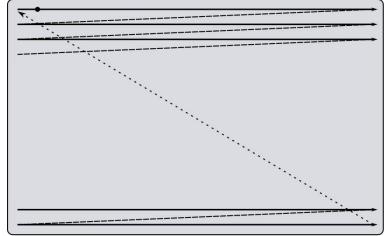

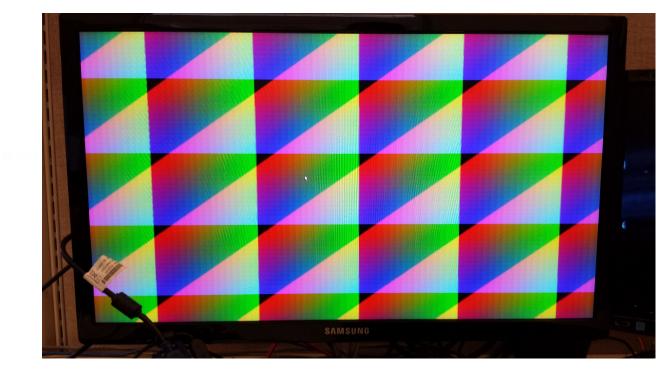

- Modern day graphics are predominantly digital (HDMI, DisplayPort etc.), but analog graphics drivers are still around (VGA)

- A VGA driver is a very good challenging FPGA project that has an analog counterpart

- VGA relies on something called a raster scan →→→

- doing zig-zags on the screen and writing out the values for every pixel in 24-bit RGB in the process

- There are DACs on each color channel writing the pixel values on the screen

img src: https://projectf.io/posts/fpga-graphics/

img src: https://electronics.stackexchange.com/guestions/166757/can-reading-vga-signals-from-my-computer-harm-the-hardware

© 2024 Burak Sone

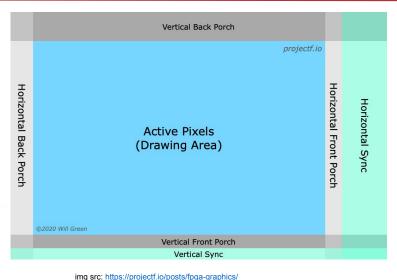

- There are addressable regions on the signal that correspond to the physical pixels on the screen as well as some "porch" areas that are included for signal processing purposes

- They increase resilience to noise and other artifacts

- The pixel clock is a fixed value, close to 25.1 MHz

- We generate this odd-valued clock via the clk\_wiz in Vivado and then get to work on the logic behind

- You can drive VGA displays to do realize arbitrary outputs this way! It's just another circuit in Vivado

0 2024 Burak Soner

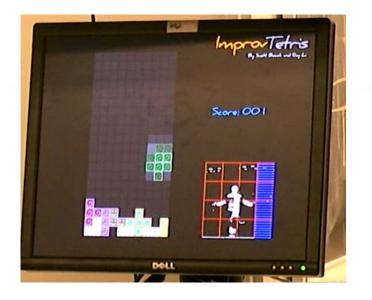

- VGA-based games are pretty fun to build and play

- These are practically your own arcade game machines!

© 2024 Burak Soner

#### Basys3 VGA demo (with a mouse):

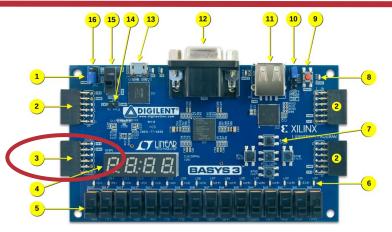

- Digilent (the company that buys FPGAs from Xilinx / AMD and builds-sells the Basys3 boards) has an example project for the Basys3 called the "GPIO Project":

- <u>https://github.com/Digilent/Basys-3-GPIO</u>

- Don't let the name fool you, the project is not for just blinking LEDs, it has simple VHDL modules for common interfaces

- 1) Switches and LEDs

- 2) Buttons and 7-segment Displays

- 3) VGA Monitor

- 4) USB Mouse

- 5) UART (actually this is a virtual COM port on a PC over USB)

- This is an important resource for your projects, which will surely use at least one of these interfaces

- Let's have a look at the website and the Vivado project

© 2024 Burak Soner

#### next → neural networks (NNs) on FPGAs

#### there's just one lab left on NNs, and a few short lectures

#### we'll heavily focus on your projects from now on